新聞中心

一、什么是ADC的孔徑延遲、它對ADC性能是否造成影響?

孔徑延遲,英文釋義為Aperture delay,是由于采樣保持開關關斷需要一定時間,相當于在采樣時鐘上引入一個小延遲,使得采集的信號為實際信號的延遲版本,因此,若孔徑延遲是固定常數,則它并不產生誤差,只會在時鐘輸入或模擬輸入中起固定延遲的作用。

但若是兩個AD轉換器同步采樣應用,由于不同AD轉換器的孔徑延遲是有差異的,可能給高擺率的信號帶來誤差,那么兩個AD轉換器必須精密匹配,必須適當調整采樣時鐘相對ADC的相位,從而消除孔徑延遲不匹配問題。

二、什么是ADC的孔徑抖動,它與孔徑延遲一樣嗎?

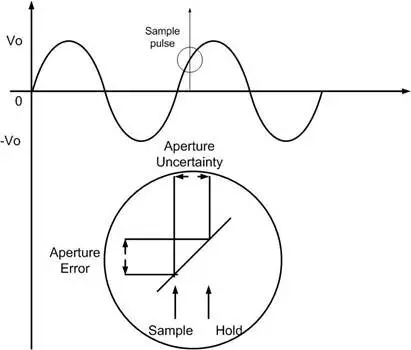

前文我們理解了孔徑延遲,若其存在樣本間變化(即,不同的輸入信號帶來不同的孔徑延遲),則會產生電壓誤差,在開關斷開時刻,這種樣本間變化稱為孔徑抖動,英文釋義為Aperture jitter,或叫孔徑不確定性英文釋義為Aperture uncertainty,如下圖所示,從而帶來孔徑抖動誤差(Aperture jitter error),用均方根皮秒(ps rms)來衡量。

圖1 孔徑抖動

三、孔徑抖動對ADC信噪比的影響

下面僅單獨考慮孔徑抖動對ADC信噪比的影響。

假定對n位的ADC輸入頻率為f的滿幅度正弦信號,表示為下式:

V(t)=V0*sin(2πft)

由于時鐘抖動引起的SNR可以簡述為下式:

SNRj=-20log2πftj

tj表示抖動時間的均方根。

可見,SNR隨輸入信號的頻率減小,但與輸入信號的幅度無關,可以簡單計算一下,一個輸入信號頻率為f=24M的ADC,它的抖動時間造成SNR降低情況如下:

tj=0.5ps,SNRj=82.45dB

tj=1ps,SNRj=76.43dB

tj=3.48ps,SNRj=65.6dB

tj=5ps,SNRj=62.45dB

可以發現,SNR隨孔徑抖動時間增加下降很快,可知其帶來的影響非常嚴重,尤其是在高速ADC應用中,其帶來的信噪比衰減更快。

芯力特電子科技有限公司(簡稱芯力特公司)是一家專業從事混合信號集成電路設計的高科技企業,有專業的ADC設計團隊,全面考慮各種非理想因素對ADC性能帶來的影響,可以為客戶定制性能優異、多種類型的ADC。公司圍繞智慧電網等物聯網致力于相關芯片技術攻關,采用靈活的商務模式提供專門的人力、物力進行技術服務與產品的定制設計,以滿足客戶的專用型需求,以一站式的服務達到客戶與自身雙贏的目的。

芯力特公司有非常優秀的AD/DA設計能力,在硅片上成功研發過多種AD,DA芯片與IP:

1)高精度高速10bit 100MHz pipeline/12bit 60MHz pipeline的ADC,已經在0.18um/0.13um CMOS工藝驗證;

2)高精度低速低功耗12bit 4MHz SAR ADC,已經在0.18um CMOS工藝驗證;

3)高精度低速的sigma-delta ADC,從14-24bit,已經在0.5um/0.35um/0.18um CMOS工藝驗證;

4)極高速的200MHz 6-8bit flash ADC,已經在0.18um/0.13um CMOS工藝驗證;

5) 8/10/12bitDAC,已經在0.35um/0.25um/0.18um/0.13umCMOS工藝驗證。

聯系方式:

聯系人:張文杰

電話:18502537108

Email:zwj@sitcores.com

網址:m.jlfute.com

掃碼二維碼關注“芯力特”微信號

地址:湖南省長沙高新開發區尖山路39號中電軟件園總部大樓

上海:上海市浦東新區豪威科技園區上科路88號

深圳:深圳市南山區科技園高新南七道1號粵美特大廈24樓

業務:15074991500(華東區),13647318510(華南區),13600008459(北西區)

服務:service@sitcores.com

招聘:tinachen@sitcores.com

Copyright ? 2020 湖南芯力特電子科技有限公司 湘ICP備2022017381號